# Выбор параметров и режимов работы МОП-транзисторов при схемотехническом моделировании аналоговых IP-компонентов Часть 1. Критерии качества МОП-транзисторов для аналоговых применений

Олег Дворников, Виталий Гришков (г. Минск, Беларусь)

Рассмотрена комбинированная модель МОП-транзистора, в которой математические соотношения, описывающие вольт-амперные характеристики, адаптированы для выполнения аналитических расчётов. На основе модели выработаны критерии качества МОП-транзисторов для аналоговых применений.

### Введение

Высококачественные функционально завершенные блоки и макроблоки, т.н. IP-компоненты (Intellectual Property – интеллектуальная собственность), являются основой для создания систем на кристалле, проектирование которых обычно выполняется на уровне соединений ранее апробированных блоков без изменения их внутренней структуры [1]. Поскольку цифровые блоки целесообразно выполнять на КМОП-транзисторах, системы на кристалле и входящие в них аналоговые IP-компоненты чаще всего изготавливают по МОП-технологиям.

Переход к субмикронным размерам усложняет проектирование аналоговых компонентов ИС. Так, МОП-транзисторы с малой длиной затвора имеют большую малосигнальную передаточную проводимость (крутизну). В то же время, они обладают рядом недостатков, ограничивающих их применение в аналоговых блоках, а именно: значительным разбросом порогового напряжения и удельной крутизны, приводящим к появлению большого напряжения смещения операционных и дифференциальных усилителей; высоким уровнем низкочастотного шума типа 1/f; нестабильностью рабочего режима вследствие температурного и временного дрейфа порогового напряжения; малой величиной выходного малосигнального сопротивления и усиления каскадов с активной нагрузкой. Небольшие размеры транзисторов приводят к уменьшению пробивного напряжения и росту токов утечки, что вынуждает снижать напряжение питания и ухудшает отношение сигнал/шум.

Особо актуальным и трудоёмким является выбор параметров и режимов работы МОП-транзисторов, ВАХ которых различны в линейной области и области насыщения, в режиме сильной и слабой инверсии, для длинноканальных и короткоканальных транзисторов. В этой связи параметрическая оптимизация схем на МОП-транзисторах превращается в многофакторный процесс, занимающий продолжительное время даже при использовании современных средств автоматизированного проектирования.

Для ускорения разработки аналоговых схем часто применяют аналитические расчёты на основе упрощённых математических соотношений, позволяющие качественно изучить поведение блоков и узлов ИС в зависимости от параметров элементов, чтобы повысить эффективность машинного моделирования [2]. В работах [3 – 5] приведе-

ны математические соотношения, связывающие характеристики схем на МОП-транзисторах с конструктивнотехнологическими параметрами, и правила проектирования, базирующиеся на опыте создания аналоговых микросхем. Так, для реализации аналоговых ИС предлагается выбирать длину затвора МОП-транзистора в 2...5 раз большую, чем минимально возможная, а превышение порогового напряжения – около 5% напряжения питания. К сожалению, эти рекомендации носят общий характер и не позволяют проектировать аналоговые устройства с требуемым приоритетом в параметрах (микромощные, прецизионные или широкополосные).

Необходимые для разработки ИС данные обычно содержатся в описании маршрута проектирования, так называемом Process Design Kit (PDK), создаваемом на предприятиях-изготовителях. Например, фирмы Taiwan Semiconductor Manufacturing International Corporation, Semiconductor Manufacturing International Corporation включают в свои PDK информацию о применяемых моделях активных и пассивных элементов, параметрах моделей, сравнительных результатах моделирования и измерений основных зависимостей МОП-транзисторов с различными размерами [6 – 8].

Несмотря на то что содержащиеся в PDK параметры моделей вполне адекватно описывают поведение интегральных элементов, разработчикам микросхем необходимы конкретные рекомендации по выбору размеров транзисторов и режимов их работы

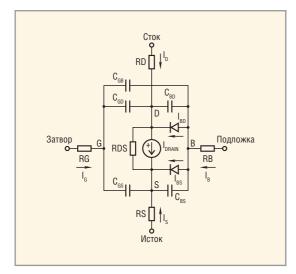

Рис. 1. Эквивалентная электрическая схема п-канального МОП-транзистора

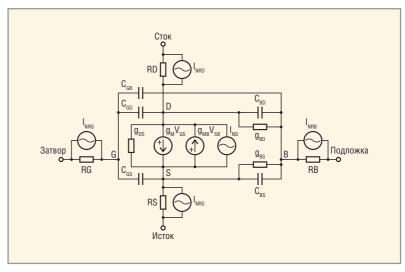

Рис. 2. Малосигнальная эквивалентная электрическая схема п-канального МОП-транзистора, включающая источники шума

для получения требуемого сочетания усиление/потребляемая мощность/полоса пропускания.

Таким образом, для ускорения схемотехнического моделирования и параметрической оптимизации целесообразно использовать критерии качества в виде упрощённых математических соотношений и/или результаты моделирования, показывающие связь основных характеристик аналоговых схем с параметрами и режимом работы МОП-транзисторов.

Целью настоящей статьи является адаптация модели МОП-транзистора для выполнения упрощённых аналитических расчётов, разработка на её основе критериев качества, определение целесообразной последовательности этапов схемотехнического моделирования, рассмотрение особенностей описания и моделирования схем на МОП-транзисторах в системе проектирования ОгСАD.

# Комбинированная модель МОП-транзистора

Для машинного моделирования обычно применяют физико-топологические и электрические модели. Физико-топологическая модель описывает поведение элемента ИС, используя конструктивно-технологические и электрофизические параметры, а элементами в электрической модели являются диоды, источники тока и напряжения, сопротивления, ёмкости, индуктивности или их сочетания. Исследование поведения аналоговых устройств аналитическими методами призвано выявить факторы, преимущественно влияющие на требуемые характеристики. При этом от моделей

элементов требуется максимальная простота, доступность для аналитических расчётов, но в тоже время учёт интегральной реализации. Для этих задач целесообразно использовать комбинированные модели [2], в основе которых лежат электрические модели, причём ряд параметров определяются, исходя из конструктивно-технологических и электрофизических параметров, как в физико-топологических моделях.

На основе анализа наиболее распространённых Spice-моделей [4, 5, 9] авторами предложена комбинированная модель МОП-транзистора, адаптированная для аналитических расчётов. Эквивалентная электрическая схема, соответствующая предложенной мо-

дели, приведена на рисунке 1, а малосигнальная электрическая схема с источниками шума — на рисунке 2. Положительным считается ток, втекающий в транзистор. Здесь и далее соотношения относятся к n-канальному транзистору (n-МОП).

Для р-канального МОП-транзистора (р-МОП) необходимо инвертировать знаки всех напряжений и токов. При «ручных» расчётах целесообразно ток стока как п-МОП, так и р-МОП считать положительным и для описания характеристик р-МОП применять соотношения п-МОП с учётом изменения полярности напряжения путём перестановки нижних индексов, описывающих выводы. Например, напряжения  $V_{\rm DS}$ ,  $V_{\rm GS}$  в соотношениях для п-МОП необ-

ходимо изменить на  $V_{\mathrm{SD}}, V_{\mathrm{SG}}$  для р-МОП транзисторов.

В соответствии с моделью, для «внутреннего» транзистора не учитывается падение напряжения на полупроводниковых областях и справедливы соотношения [9]:

$$I_{G} = 0, \tag{1}$$

$$I_{B} = I_{BS} + I_{BD} = AS JS \left( \exp \frac{V_{BS}}{N \varphi_{T}} - 1 \right) +$$

$$+AD JS \left(\exp \frac{V_{\rm BD}}{N\varphi_{\rm T}} - 1\right),$$

(2)

$$I_{\rm D} = I_{\rm DRAIN} - AD JS \left( \exp \frac{V_{\rm BD}}{N \varphi_{\rm T}} - 1 \right), \quad (3)$$

$$I_{\rm S} = -AS JS \left( \exp \frac{V_{\rm BS}}{N \phi_{\rm T}} - 1 \right) - I_{\rm DRAIN} , \quad (4)$$

где  $I_{\rm G}, I_{\rm B}, I_{\rm D}, I_{\rm S}, I_{\rm DRAIN}, I_{\rm BS}, I_{\rm BD}$  — ток затвора, подложки (body), стока, истока, генератора тока и диодов эквивалентной схемы; AS, AD — площадь полупроводниковой области истока, стока; JS — плотность тока насыщения подложка-сток (исток);  $V_{\rm BS}, V_{\rm BD}$  — напряжение на внутренних р—п-переходах подложка-исток, подложка-сток; N — фактор, характеризующий отклонение BAX от экспоненты;  $\phi_{\rm T} = kT/q$  — температурный потенциал; q — заряд электрона; k — постоянная Больцмана, k = 1,38 × 10<sup>-23</sup> Дж/К; T — абсолютная температура.

Кроме того, на рисунке 1 расположен резистор RDS, который описывает сопротивление утечки сток-исток. Величина тока  $I_{\rm DRAIN}$  различается для режима сильной (strong,  $V_{\rm GS} > V_{\rm TH}$ ) и слабой (weak,  $V_{\rm GS} \le V_{\rm TH}$ ) инверсии. Последний режим также называется подпороговой областью.

Для длинноканальных МОП-транзисторов справедливы соотношения: • при  $V_{\rm DS} < V_{\rm GS} - V_{\rm TH}, V_{\rm GS} > V_{\rm TH}$  (линейная область BAX)

$$I_{\text{DRAIN}} = \beta \left[ (V_{\text{GS}} - V_{\text{TH}}) V_{\text{DS}} - \frac{V_{\text{DS}}^2}{2} \right], (5)$$

$$\beta = KP \frac{W}{L_{\rm EFF}}, \tag{6}$$

$$V_{\rm TH} = VTO + \gamma \left( \sqrt{2\,\varphi_{\rm F} - V_{\rm BS}} - \sqrt{2\,\varphi_{\rm F}} \right); (7)$$

при V<sub>DS</sub> ≥ V<sub>GS</sub> − V<sub>TH</sub>, V<sub>GS</sub> > V<sub>TH</sub> (область насыщения ВАХ)

$$I_{\text{DRAIN}} = \frac{\beta}{2} \left[ 1 + \lambda \left( V_{\text{DS}} - V_{\text{DSAT}} \right) \right] \left( V_{\text{GS}} - V_{\text{TH}} \right)^2, \tag{8}$$

$$V_{\rm DSAT} = V_{\rm GS} - V_{\rm TH}; \tag{9}$$

• при  $V_{\rm DS}$  ≥  $4\phi_{\rm T}$ ,  $V_{\rm GS}$  <  $V_{\rm TH}$  −  $4\phi_{\rm T}$  (область насыщения ВАХ в слабой инверсии)

$$I_{\mathrm{DRAINW}} = \beta \phi_{\mathrm{T}}^{2} \exp 1.8 \exp \frac{V_{\mathrm{GS}} - V_{\mathrm{TH}}}{N_{\mathrm{W}} \phi_{\mathrm{T}}} =$$

$$=I_{\rm DOW}\exp\frac{V_{\rm GS}-V_{\rm TH}}{N_{\rm W}\phi_{\rm T}},\qquad (10)$$

• для короткоканальных МОП-транзисторов при  $V_{\rm DS} \ge V_{

m DSATSH}, V_{

m GS} > V_{

m TH}$  (область насыщения ВАХ) выполняется

$$I_{\text{DRAINSH}} = Wv_{\text{SAT}}C_{\text{OX}}[1+\lambda_{\text{SH}}(V_{\text{DS}} - V_{\text{DSATSH}})](V_{\text{GS}} - V_{\text{TH}} - V_{\text{DSATSH}}), (11)$$

где β - удельная крутизна передаточной характеристики, λ - коэффициент, характеризующий выходную проводимость в области насыщения ВАХ, Для длинноканальных транзисторов λ ~ 1/LEFF – коэффициент модуляции длины канала напряжением  $V_{\rm DS}$ , для короткоканальных транзисторов величина определяется влиянием нескольких факторов, в том числе модуляцией подвижности носителей заряда, обычно  $\lambda$  = 0,01...0,1;  $V_{\mathrm{GS}}, V_{\mathrm{DS}}, V_{\mathrm{BS}}$  – напряжение затвор-исток, сток-исток, подложка-исток;  $V_{\mathrm{DSAT}}$  – напряжение стокисток, соответствующее переходу из линейной области ВАХ к области насыщения, которое для короткоканальных транзисторов ( $V_{\mathrm{DSATSH}}$ ) обычно меньше, чем для длинноканальных, т.е.  $V_{\mathrm{D-}}$  $_{\rm SATSH}$  <  $V_{\rm GS}$  –  $V_{\rm TH}$  ;  $V_{\rm TH}$  – пороговое напряжение при  $V_{\rm BS}$   $\neq$  0; VTO – пороговое напряжение при  $V_{BS}$  = 0; KP =  $\mu_{COX}$  – удельная крутизна при управлении затвором,  $C_{\rm OX}$  =  $\varepsilon_{\rm OX}/TOX$  – удельная ёмкость подзатворного окисла, и - подвижность основных носителей заряда в канале МОП-транзистора,  $\varepsilon_{\rm OX}$  = 3,9 $\varepsilon_0$  = =  $3.9 \times 8.85 \times 10^{-18} \, \Phi$ /мкм – диэлектрическая проницаемость окисла кремния,  $\varepsilon_0$  – абсолютная диэлектрическая проницаемость, ТОХ - толщина подзатворного окисла; W, L – ширина и длина затвора;  $L_{\text{EFF}} = L - 2LD - эффек$ тивная длина затвора, LD - величина боковой диффузии;  $I_{\mathrm{DRAINW}}$  – ток генератора эквивалентной схемы в подпороговой области ВАХ;  $I_{\mathrm{D0W}}$  – ток стока при пороговом напряжении, т.е.  $I_{\rm DOW}$  = =  $I_{\rm D}$  при  $V_{\rm GS}$  =  $V_{\rm TH}$ ;  $N_{\rm W}$  – фактор, характеризующий отклонение ВАХ в подпороговой области от экспоненты, обычно величина  $N_{\rm W}$  составляющей от 1 до 2;  $\gamma = (2q\varepsilon_{\rm SI}N_{\rm A})^{0.5}/C_{\rm OX}$  — коэффициент влияния потенциала подложки на пороговое напряжение (body-effect);  $\phi_{\rm F} = \phi_{\rm T} \ln(N_{\rm A}/N_{\rm I})$  — поверхностный потенциал;  $\varepsilon_{\rm SI} = 11,7\varepsilon_0$  — диэлектрическая проницаемость кремния,  $N_{\rm A}$  — концентрация ионизированных акцепторов в подложке,  $N_{\rm I}$  — собственная концентрация носителей, для кремния  $N_{\rm I}$  = 1,45× ×  $10^{-10}$  см<sup>-3</sup>;  $v_{\rm SAT}$  — скорость насыщения носителей заряда в канале.

Здесь и далее нижними индексами SH отмечены параметры короткоканального (short channel) транзистора, а индексом W – параметры в области слабой инверсии.

Соотношения (5)—(9) соответствуют модели Шихмана—Ходжеса, которая в Spice-подобных программах описывает ВАХ МОП-транзистора при указании параметра LEVEL = 1, а соотношения (10), (11) — BSIM-модели при задании параметра LEVEL = 4, 6, 7.

Обычно МОП-транзисторы применяются при обратном смещении p—пперехода исток-подложка. При этом для n-канальных приборов  $V_{\rm BS} \! \le \! 0$ , а  $V_{\rm SB} \! = \! -V_{\rm BS} \! > \! 0$ , и (7) целесообразно представить в виде:

$$V_{\rm TH} = VTO + \gamma \Big( \sqrt{2\,\varphi_{\rm F} + V_{\rm SB}} - \sqrt{2\,\varphi_{\rm F}} \,\Big). \eqno(12)$$

Малосигнальная эквивалентная электрическая схема включает следующие элементы (малым считается переменный сигнал  $v_{\rm GS}$ ,  $i_{\rm D}$ , который намного меньше постоянного  $V_{\rm GS}$ ,  $I_{\rm D}$ , определяющего рабочую точку, т.е.  $|v_{\rm GS}|$  <<  $|V_{\rm GS}|$ ,  $|i_{\rm D}|$  <<  $|I_{\rm D}|$ ):

$$g_{\rm BD} = \frac{\mathrm{d}I_{\rm BD}}{\mathrm{d}V_{\rm BD}},\tag{13}$$

$$g_{\rm BS} = \frac{\mathrm{d}I_{\rm BS}}{\mathrm{d}V_{\rm BS}};\tag{14}$$

при  $V_{

m DS}$   $\geq$   $V_{

m GS}$  -  $V_{

m TH}$ ,  $V_{

m GS}$  >  $V_{

m TH}$

$$g_{\rm M} = \frac{{\rm d}I_{\rm DRAIN}}{{\rm d}V_{\rm GS}} \approx \beta V_{\rm DSAT} \approx \sqrt{2\beta I_{\rm DRAIN}}$$

,(15)

$$g_{\rm MB} = -\frac{{\rm d}I_{\rm DRAIN}}{{\rm d}V_{\rm SB}} \approx \beta V_{\rm DSAT} \; \frac{{\rm d}V_{\rm TH}}{{\rm d}V_{\rm SB}} =$$

$$=\frac{g_{\rm M}\gamma}{\sqrt{2\varphi_{\rm F}+V_{\rm SB}}}=\eta g_{\rm M},\qquad (16)$$

$$g_{\rm DS} = \frac{\mathrm{d}I_{\rm DRAIN}}{\mathrm{d}V_{\rm DS}} = \frac{\beta}{2} (V_{\rm GS} - V_{\rm TH})^2 \lambda = I_{\rm DSAT} \lambda, \tag{17}$$

$$I_{\text{DSAT}} = I_{\text{DRAIN}} \Big|_{V_{\text{DS}} = V_{\text{DSAT}}} = \frac{\beta}{2} V_{\text{DSAT}}^2, (18)$$

$$g_{\text{MSH}} = W v_{\text{SAT}} C_{\text{OX}} [1 + \lambda_{\text{SH}} (V_{\text{DS}} - V_{\text{DSATSH}})] \approx W v_{\text{SAT}} C_{\text{OX}}, \quad (19)$$

$$g_{\text{DSSH}} = W v_{\text{SAT}} C_{\text{OX}} \lambda_{\text{SH}} (V_{\text{GS}} - V_{\text{TH}} - V_{\text{DSATSH}}) = I_{\text{DSATSH}} \lambda_{\text{SH}}, \quad (20)$$

$$I_{\text{DSATSH}} = I_{\text{DRAINSH}} \Big|_{V_{\text{DS}} = V_{\text{DSATSH}}} =$$

$$= W v_{\text{SAT}} C_{\text{OX}} (V_{\text{GS}} - V_{\text{TH}} - V_{\text{DSATSH}}); \quad (21)$$

при

$$V_{\rm DS}$$

$<$   $V_{\rm GS}$   $V_{\rm TH}$ ,  $V_{\rm GS}$   $>$   $V_{\rm TH}$

$$g_{\rm ML} = \frac{{\rm d}I_{\rm DRAIN}}{{\rm d}V_{\rm GS}} = \beta V_{\rm DS} \,, \eqno(22)$$

$$g_{\text{MBL}} = -\frac{dI_{\text{DRAIN}}}{dV_{\text{SB}}} = \beta V_{\text{DS}} \frac{dV_{\text{TH}}}{dV_{\text{SB}}} = \eta g_{\text{ML}}, (23)$$

$$g_{\rm DSL} = \frac{\mathrm{d}I_{\rm DRAIN}}{\mathrm{d}V_{\rm DS}} = \frac{1}{R_{\rm CH}} = \beta \left(V_{GS} - \frac{1}{R_{\rm CH}}\right)$$

$$-V_{\text{TH}} - V_{\text{DS}}$$

) =  $\beta (V_{\text{DSAT}} - V_{\text{DS}})$ , (24)

$$g_{\mathrm{DSL}} \approx \beta V_{\mathrm{DSAT}} pprox g_{\mathrm{M}}$$

при  $|V_{\mathrm{DS}}| << |V_{\mathrm{DSAT}}|; (25)$

при

$$V_{

m DS} \! \geq \! 4\phi_{

m T}, V_{

m GS} \! < \! V_{

m TH} - \! 4\phi_{

m T}$$

$$g_{\text{MW}} = \frac{dI_{\text{DRAINW}}}{dV_{\text{GS}}} =$$

$$=\frac{\beta\phi_{\mathrm{T}}^{2}\exp\mathbf{1.8}\exp\frac{V_{\mathrm{GS}}-V_{\mathrm{TH}}}{N_{\mathrm{W}}\phi_{\mathrm{T}}}}{N_{\mathrm{W}}\phi_{\mathrm{T}}}=$$

$$=\frac{I_{\text{DRAINW}}}{N_{\text{W}}\,\varphi_{\text{T}}},\tag{26}$$

$$g_{\text{MBW}} = -\frac{dI_{\text{DRAINW}}}{dV_{\text{SB}}} =$$

$$= \frac{\beta \phi_{\rm T}^2 \exp 1.8 \exp \frac{V_{\rm GS} - V_{\rm TH}}{N_{\rm W} \phi_{\rm T}}}{N_{\rm W} \phi_{\rm T}} \frac{dV_{\rm TH}}{dV_{\rm SB}} = \frac{1}{100} \frac{1}{100} = \frac{$$

$$g_{\text{DSW}} \approx I_{\text{DRAINW}} \lambda_{\text{W}},$$

(28)

$$\eta = \frac{dV_{\text{TH}}}{dV_{\text{SB}}} = \frac{\gamma}{\sqrt{2\,\varphi_{\text{F}} + V_{\text{SB}}}} = \frac{C_{\text{DEP}}}{C_{\text{OX}}}, (29)$$

где  $g_{\rm BD}, g_{\rm BS}$  – малосигнальная проводимость диодов эквивалентной схемы;  $g_{\rm M}, g_{\rm MW}$  – малосигнальная передаточная проводимость (крутизна) при управлении затвором в режиме сильной и слабой инверсии;  $g_{\rm MB}, g_{\rm MBW}$  – крутизна при управлении подложкой в режиме сильной и слабой инверсии.

Знак минус в выражениях (16), (27) учитывает тот факт, что изменение тока стока, вызванное изменением потенциала подложки, имеет противоположный характер по отношению к изменению тока стока, вызванному изменением потенциала затвора. Принято считать  $g_{\rm M}$  и g<sub>MB</sub> положительными величинами и описывать указанный эффект противоположным направлением тока источника  $g_{M}v_{GS}$  на рисунке 2 по сравнению с  $g_{MB}v_{SB}$ ;  $g_{\mathrm{DS}}, g_{\mathrm{DSL}}$  – малосигнальная выходная проводимость в насыщении и линейной области в режиме сильной инверсии ( $g_{DSSH}$ для короткоканальных транзисторов сильно зависит от  $V_{\mathrm{DS}}$ );  $g_{\mathrm{DSW}}$  – малосигнальная выходная проводимость в насыщении в режиме слабой инверсии, соотношение (28) получено из (17) путём замены  $I_{\mathrm{DSAT}}$  на  $I_{\mathrm{DRAINW}}$ ,  $\lambda$  на  $\lambda_{\mathrm{W}}$  с учётом того, что параметр  $\lambda_W$  определяется экспериментально и ток стока в области насыщения является постоянным в режиме слабой инверсии при  $V_{DS}$  ≥  $4\phi_T$ ;  $R_{CH}$  – сопротивление канала МОП-транзистора при  $V_{

m DS}\!<\!V_{

m GS}\!-\!V_{

m TH},V_{

m GS}\!>\!V_{

m TH};C_{

m DEP}\!-\!{

m yge}$ льная ёмкость р-п-перехода канал-подложка,  $d_{\rm OH3}$  – ширина области пространственного заряда р-п-перехода канал-

$$d_{\rm OH3} = \left[ \frac{2 \, \varepsilon_{\rm SI}}{a N_{\rm A}} \left( \phi_{\rm F} - V_{\rm PN} \right) \right]^{MJ};$$

$V_{

m PN}$  – напряжение на р<br/>– п-переходе канал-подложка (положительное при

прямом смещении и отрицательное при обратном); MJ – показатель степени в зависимости барьерной ёмкости от обратного напряжения.

В соотношениях (22)–(25) и далее нижний индекс L указывает на принадлежность параметра к линейной области ВАХ, в которой МОП-транзистор функционирует как резистор, управляемый напряжением  $V_{\rm GS}-V_{\rm TH}$ . Величины ёмкостей эквивалентной схемы в зависимости от режима работы показаны в таблице.

Обычно при проектировании схем на МОП-транзисторах не применяют режим работы с прямым смещением р-п-переходов между истоком (стоком) и подложкой, поэтому в последующих разделах мы полагаем  $I_{DRAIN} = I_D$ .

# Критерии качества МОП-транзисторов для аналоговых применений

Анализ соотношений (15) – (29) и литературных данных позволил сделать ряд выводов по выбору режимов работы, топологических размеров МОП-транзисторов для конкретных аналоговых применений.

1. Для выбора типа активного элемента аналоговых микросхем целесообразно сравнить быстродействие транзисторов по граничной частоте  $f_{\rm T}$ , на которой переменный сигнал, протекающий через вход активного элемента, равен переменному сигналу, протекающему в выходной цепи при условии короткого замыкания выходной цепи по переменному сигналу. Для биполярных транзисторов  $f_{\rm T}$  соответствует частоте, на которой модуль малосигнального коэффициента передачи тока в схеме с общим эмиттером равен единице ( $|b_{21e}|$  = =  $|i_{\rm C}/i_{\rm B}|$  = 1) при подключении коллектора к источнику постоянного напряжения (малое внутреннее сопротивление по переменному сигналу источника напряжения обеспечивает режим короткого замыкания по переменному сигналу в выходной цепи).

Математические соотношения, описывающие влияние конструктивно-технологических параметров на граничную частоту биполярных транзисторов, известны и приведены в [10-12]. Для вертикальных биполярных транзисторов  $f_{\rm T}$  определяется временем пролёта носителей заряда через базу, которое не масштабируется при изменении тополо-

### Величины емкостей эквивалентной схемы, показанной на рисунке 2 [3]

| Параметр           | Режим работы для n-MOП                      |                                                                          |                                                                                             |

|--------------------|---------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|                    | V <sub>GS</sub> ≤ V <sub>TH</sub>           | $V_{\rm DS}$ < $V_{\rm GS}$ - $V_{\rm TH}$ , $V_{\rm GS}$ > $V_{\rm TH}$ | $V_{\mathrm{DS}} \geq V_{\mathrm{GS}} - V_{\mathrm{TH}}, V_{\mathrm{GS}} > V_{\mathrm{TH}}$ |

| $\mathcal{C}_{GD}$ | CGDO W                                      | 0,5 <i>W L C</i> <sub>0X</sub>                                           | CGDO W                                                                                      |

| $C_{BD}$           | $C_{DEP}\!AD$                               | $C_{DEP} AD$                                                             | $C_{DEP} AD$                                                                                |

| $\mathcal{C}_GB$   | W L <sub>EFF</sub> C <sub>OX</sub> + CGBO L | CGBO L                                                                   | CGBO L                                                                                      |

| $\mathcal{C}_{GS}$ | CGSO W                                      | 0,5 <i>W L C</i> <sub>0X</sub>                                           | 2W L C <sub>OX</sub> /3                                                                     |

| $\mathcal{C}_{BS}$ | $C_{DEP}\!AS$                               | $C_{DEP} AS$                                                             | $C_{DEP}\!AS$                                                                               |

$C_{\rm GS}, C_{\rm GD}, C_{\rm GB}$  — ёмкость затвор-исток, затвор-сток, затвор-подложка,  $C_{\rm BD}, C_{\rm BS}$  — ёмкость р—п-перехода подложка-сток, подложка-исток,  $C_{\rm GD}$ 0 =  $C_{\rm OX}$ LD — удельная ёмкость перекрытия затвор-сток (на единицу ширины канала) за счёт боковой диффузии,  $C_{\rm GSO}$  =  $C_{\rm OX}$ LD — удельная ёмкость перекрытия затвор-исток (на единицу ширины канала) за счёт боковой диффузии,  $C_{\rm GSO}$ 0 — удельная ёмкость перекрытия затвор-подложка за счёт выхода затвора за пределы канала

гических размеров транзистора. Изменение площади эмиттера приводит, в основном, к сдвигу максимума зависимости граничной частоты от эмиттерного тока.

Для МОП-транзисторов  $f_{\rm T}$  соответствует частоте, на которой  $|i_{\rm D}|=|i_{\rm G}|$ , и допускает масштабирование изменением топологических размеров затвора.

На основании рисунка 2, соотношений (15), (19) и данных таблицы получим:

$$f_{\rm T} \approx \frac{g_{\rm M}}{2\pi C_{\Sigma G}},$$

(30)

$$f_{\rm T} = \frac{KPW(V_{\rm GS} - V_{\rm TH})}{2\pi I_{\rm EFF} (C_{\rm GB} + C_{\rm GS} + C_{\rm GD})}, (31)$$

$$f_{\mathrm{T}} pprox rac{3 \mathit{KP} \left(V_{\mathrm{GS}} - V_{\mathrm{TH}} \right)}{4 \pi \mathcal{L}_{\mathrm{EFF}}^2 \, C_{\mathrm{OX}}} = rac{3 \mu}{4 \pi} rac{\left(V_{\mathrm{GS}} - V_{\mathrm{TH}} \right)}{\mathcal{L}_{\mathrm{EFF}}^2}$$

при  $C_{\mathrm{GS}} >> C_{\mathrm{GB}} + C_{\mathrm{GD}}$ , (32)

$$f_{\mathrm{TSH}} pprox rac{3}{4 \pi \mathcal{L}_{\mathrm{EFF}}}$$

при

$$C_{GS} >> C_{GB} + C_{GD}$$

, (33)

где  $C_{\Sigma G}$  – суммарная ёмкость, соединённая с затвором. Соотношения (31) – (33) справедливы для области насыщения ВАХ, причём (31) – (32) – для длинноканальных, а (33) – для короткоканальных транзисторов.

Таким образом, граничная частота  $f_{\rm T}$  длинноканальных МОП-транзисторов, работающих в области насыщения ВАХ, не зависит от ширины затвора, обратно пропорциональна квадрату длины затвора и прямо пропорциональна разности напряжений затвор-исток и порогового напряжения  $V_{\rm GS}-V_{\rm TH}$ . Для короткоканальных МОП-транзисторов в области насыщения  $f_{\rm TSH}$  обратно пропорциональна длине затвора и не зависит от напряжения затвора.

2. Максимально возможный коэффициент усиления  $K_{\rm MAX}$  каскада на МОП-транзисторе с общим истоком, в предположении бесконечно большой нагрузки в стоковой цепи, составит для длинноканального транзистора:

$$K_{\rm MAX} = \frac{v_{\rm DS}}{v_{\rm GS}} = -\frac{g_{\rm M}}{g_{\rm DS}} =$$

$$=-g_{\rm M}r_{\rm OUT}\approx-\frac{\sqrt{2\beta}}{\lambda\sqrt{I_{\rm D}}},\qquad(34)$$

$$K_{\rm MAX} \approx -\frac{2}{\left(V_{\rm GS} - V_{\rm TH}\right)\lambda},$$

(35)

$$K_{\text{MAXW}} \approx -\frac{1}{N_{\text{W}} \varphi_{\text{T}} \lambda_{\text{W}}};$$

(36)

для короткоканального транзистора:

$$K_{\text{MAXSH}} \approx -\frac{1}{\lambda_{\text{SH}} \left( V_{\text{GS}} - V_{\text{TH}} - V_{\text{DSATSH}} \right)}, (37)$$

где

$$r_{\text{OUT}} = \frac{1}{g_{\text{DS}}}$$

– выходное малосиг-

нальное сопротивление в области насыщения BAX.

Знак минус в выражениях (34) – (37) указывает на то, что каскад с общим истоком является инвертирующим усилителем напряжения.

На основании (34), (35) можно утверждать, что для длинноканального транзистора при заданном токе стока  $K_{\rm MAX} \sim \sqrt{L_{\rm EFF}}$ , а при заданном напряжении  $V_{\rm GS} - V_{\rm TH}$  справедливо условие  $K_{\rm MAX} \sim L_{\rm EFF}$ .

Полученные соотношения (32) – (37) позволяют рассчитать т.н. коэффициент качества (figure of merit), равный произведению граничной частоты на коэффициент усиления напряжения при разомкнутой цепи стока:

$$f_{\rm T} K_{\rm MAX} \approx \frac{3\mu}{2\pi} \frac{1}{I_{\rm EFF}^2 \lambda} \sim \frac{1}{I_{\rm EFF}}, (38)$$

$$f_{TSII}K_{MAXSII} \approx$$

$$\approx \frac{3}{4\pi} \frac{v_{\text{SAT}}}{L_{\text{EFF}} \lambda_{\text{SH}} \left( V_{\text{GS}} - V_{\text{TH}} - V_{\text{DSATSH}} \right)}. (39)$$

Таким образом, для длинноканальных МОП-транзисторов произведение  $f_{\rm T}K_{\rm MAX}$  не зависит от рабочего режима. Увеличение полосы пропускания каскадов за счёт увеличения напряжения на затворе приводит к уменьшению усиления и диапазона напряжения сток-исток, в котором транзистор работает в области насыщения ВАХ и обеспечивается высокое усиление.

3. Коэффициент усиления каскада K с общим истоком в области низких частот при работе с реальной нагрузкой определяется крутизной МОПтранзистора и суммарным сопротивлением всех цепей  $R_{\Sigma D}$ , соединённых со стоком, т.е.  $K \approx R_{\Sigma D} g_{\rm M}$ . В этой связи при выборе требуемого сочетания усиления и тока потребления рекомендуется обращать внимание

на отношение  $g_{\rm M}/I_{\rm D}$  в режиме сильной и слабой инверсии:

$$\frac{g_{\rm M}}{I_{\rm D}} = \sqrt{\frac{2\beta}{I_{\rm D}}} , \qquad (40)$$

$$\frac{g_{\text{MW}}}{I_{\text{DW}}} = \frac{1}{N_{\text{W}} \varphi_{\text{T}}}.$$

(41)

Для типовых величин ( $N_{

m W}$  от 1 до  $2, \phi_T = 26 \text{ мВ при } 300^{\circ}\text{K})$  отношение  $g_{\rm M}/I_{\rm D}$  в подпороговой области будет в диапазоне от 19 до 39, что значительно больше, чем для квадратичной области ВАХ. При использовании МОП-транзисторов в подпороговой области необходимо учитывать, что экспоненциальная зависимость тока стока от напряжения затвор-исток может вызвать большую неидентичность рабочих токов и значительно ухудшить напряжение смещения ОУ. Другим фактором, вызывающим различие характеристик каскадов на МОП-транзисторах, работающих в режиме слабой инверсии, является технологический разброс слабо контролируемого параметра  $N_{\mathrm{W}}$ . Заметим, что увеличение отношения W/L МОПтранзисторов приводит к росту β и величины максимального тока стока  $I_{\rm DOW}$ , при котором транзистор работает в подпороговой области ВАХ (cm. (6), (10)).

Увеличение обратного напряжения исток-подложка V<sub>SB</sub> приводит к уменьшению тока стока, крутизны, увеличению порогового напряжения V<sub>TH</sub>. Однако при этом уменьшается влияние технологического разброса параметров на ВАХ и приведённый к затвору МОП-транзистора шум подложки [13]. Такой режим работы целесообразно применять в ОУ для уменьшения уровня шума и напряжения смещения нуля.

При проектировании топологии необходимо учитывать, что область полупроводника (body), в которой индуцируется токопроводящий канал МОП-транзистора, может быть как общей для всех элементов ИС полупроводниковой подложкой (substrate), так и областью кармана (well), изолированного от остальных элементов схемы. В технологических маршрутах изготовления МОП ИС с «карманом п-типа» канал в пканальных МОП-транзисторах индуцируется в единой для всех эле-

ментов схемы р-подложке, поэтому вывод b п-МОП-транзистора всегда соединён с самым отрицательным потенциалом схемы, в то же время, вывод b р-МОП может быть подключен к нужному узлу. Только технологические маршруты с «формированием двух карманов» предоставляют возможность соединения вывода b как п-канальных, так и р-канальных МОП-транзисторов с требуемыми узлами схемы.

5. Выходной импеданс истокового повторителя  $Z_{\rm OUTS}$  может быть представлен как последовательное соединение резистора с номиналом  $1/g_{\rm M}$  и индуктивности величиной:

$$\frac{\mathit{R}_{\Sigma\mathrm{G}}\left(\mathit{C}_{\mathrm{GB}}+\mathit{C}_{\mathrm{GS}}+\mathit{C}_{\mathrm{GD}}\right)}{\mathit{g}_{\mathrm{M}}},$$

T.e.

$$Z_{\rm OUTS} = \frac{1}{g_{\rm M}} \Big[ 1 + j 2 \pi f R_{\Sigma \rm G} \, \left( C_{\rm GB} + \frac{1}{2} \right) \Big] + \frac{1}{2} \left( C_{\rm GB} + \frac{1}{2} \right) \Big] + \frac{1}{2} \left( C_{\rm GB} + \frac{1}{2} \right) \left( C_{\rm GB} + \frac{1}{2} \right) \Big]$$

$$+C_{GS}+C_{GD}), \qquad (42)$$

где  $R_{\Sigma G}$  – суммарное сопротивление всех параллельных цепей между за-

твором и узлами с нулевым переменным потенциалом («заземлением» по переменному току, «AC ground»); f – частота.

Таким образом, если истоковый повторитель управляется высокоомным источником сигнала, то выходной импеданс повторителя имеет индуктивный характер, что может вызвать колебания при работе повторителя с емкостной нагрузкой. Если импеданс источника, соединённого с затвором, индуктивный, например, в случае двух последовательно соединённых истоковых повторителей, то выходной импеданс второго повторителя может быть отрицательным, и возможно самовозбуждение при работе с любой нагрузкой.

## Литература

- 1. *Адамов Ю.Ф.* Системы на кристалле в современной электронике. Микросистемная техника. 2004. № 5. С. 34–38.

- 2. Абрамов И.И. Проектирование аналоговых микросхем для прецизионных измерительных систем. Минск: Акад. упр. при Президенте Респ. Беларусь, 2006.

- 3. *Baker R.J.* CMOS. Circuit design, layout and simulation. N.Y., IEEE Pres, 1998.

- 4. *Baker R.J.* CMOS. Circuit design, layout and simulation. Piscataway, IEEE Pres, 2005.

- Эннс В.И. Проектирование аналоговых КМОП-микросхем. Горячая линия-Телеком, 2005.

- 6. TSMC 0.18um mixed signals/RF 1P6M salicide 1.8V/3.3V design rule.

- 7. TSMC 0.18um mixed signals 1P6M salicide 1.8V/3.3V SPICE models.

- 8. SMIC 0.13 um 1.2/3.3V Mix&RF, SMIC 0.13 um MM 1P8M salicide PDKs.

- Pspice. Reference Guide. Mode of access (http://www.orcad.com).

- Бубенников А.Н. Физико-технологическое проектирование биполярных элементов кремниевых БИС. Радио и связь, 1991.

- 11. *Зи С.* Физика полупроводниковых приборов: Кн. 1. Мир, 1984.

- 12. *Маллер Р*. Элементы интегральных схем. Мир, 1989.

- 13. Beuville E. AMPLEX. A low-noise, low-power analog CMOS signal processor for multielement silicon particles detectors. Nuclear Instruments and Methods in Physics Research. 1990. Vol. A288. P. 157–167.